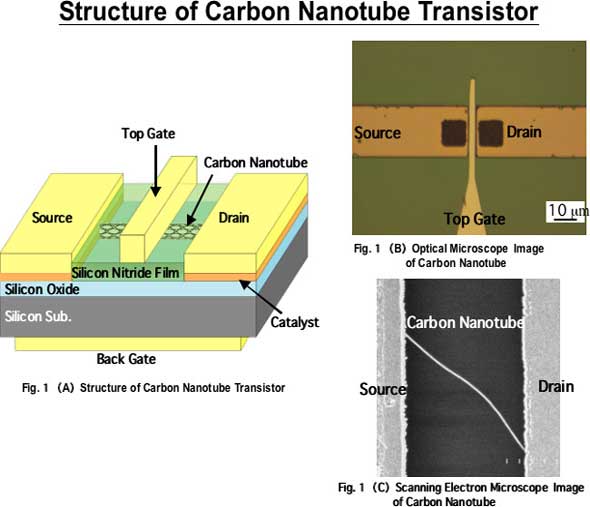

- A single semiconducting CNT can be used as the conducting channel between the source and drain of a FET. Figure 1 illustrates a back-gated Schottky barrier CNT FET. Two metal contacts are located across both ends of the CNT to form the Source and Drain terminals of the FET. The CNT is placed.

- 伍 晖 博士,副教授 办公地址:清华大学逸夫技术科学楼B320. 至2018年3月,以第一作者或通讯作者身份在Nature Chemistry, Nature Nanotechnology, Nature Communications 等学术期刊发表论文80余篇,发表论文被引用超过12000次, H因子41。.

LATEST MODELS

Typical SPICE model files for each future generation are available here.

Attention: By using a PTM file, you agree to acknowledge both the URL of PTM: http://ptm.asu.edu/and the related publicationsin all documents and publications involving its usage.

Channel CNT FET. The CNT is then covered with TiO 2 iii to form the bottom-gate covered channel CNT FET. Finally, an Al gate electrode is fabricated on top of the TiO 2 iv to form the top-gate CNT FET. B Scan-ning electron micrograph of the bottom-gated CNT FET. C Scanning elec-tron micrograph of the same device after fabricating the top-gate. Among them, Carbon Nanotube (CNT) FET, Gate-All-Around Nanowire FET or FinFETs with compound semiconductors may prove as promising solutions in future technology nodes. Hu, 'Modern Semiconductor Devices for Integrated Circuits', Pearson/Prentice Hall, New Jersey, 351 pages, 2010. 伍 晖 博士,副教授 办公地址:清华大学逸夫技术科学楼B320. 至2018年3月,以第一作者或通讯作者身份在Nature Chemistry, Nature Nanotechnology, Nature Communications 等学术期刊发表论文80余篇,发表论文被引用超过12000次, H因子41。.

New!

June 01, 2012:

PTM releases a new set of models for multi-gate transistors (PTM-MG), for both HP and LSTP applications. It is based on BSIM-CMG, a dedicated model for multi-gate devices.

Acknowledgement: PTM-MG is developed in collaboration with ARM.

Please start from models and param.inc.

- 7nm PTM-MG HP NMOS, HP PMOS, LSTP NMOS, LSTP PMOS

- 10nm PTM-MG HP NMOS, HP PMOS, LSTP NMOS, LSTP PMOS

- 14nm PTM-MG HP NMOS, HP PMOS, LSTP NMOS, LSTP PMOS

- 16nm PTM-MG HP NMOS, HP PMOS, LSTP NMOS, LSTP PMOS

- 20nm PTM-MG HP NMOS, HP PMOS, LSTP NMOS, LSTP PMOS

The entire package is also available here: PTM-MG

November 15, 2008:

PTM releases a new set of models for low-power applications (PTM LP), incorporating high-k/metal gate and stress effect.

- 16nm PTM LP model: V2.1

- 22nm PTM LP model: V2.1

- 32nm PTM LP model: V2.1

- 45nm PTM LP model: V2.1

September 30, 2008:

PTM releases a new set of models for high-performance applications (PTM HP), incorporating high-k/metal gate and stress effect.

- 16nm PTM HP model: V2.1

- 22nm PTM HP model: V2.1

- 32nm PTM HP model: V2.1

- 45nm PTM HP model: V2.1

PTM releases a new set of models for multi-gate transistors (PTM-MG), for both HP and LSTP applications. It is based on BSIM-CMG, a dedicated model for multi-gate devices.

Acknowledgement: PTM-MG is developed in collaboration with ARM.

Please start from models and param.inc.

- 7nm PTM-MG HP NMOS, HP PMOS, LSTP NMOS, LSTP PMOS

- 10nm PTM-MG HP NMOS, HP PMOS, LSTP NMOS, LSTP PMOS

- 14nm PTM-MG HP NMOS, HP PMOS, LSTP NMOS, LSTP PMOS

- 16nm PTM-MG HP NMOS, HP PMOS, LSTP NMOS, LSTP PMOS

- 20nm PTM-MG HP NMOS, HP PMOS, LSTP NMOS, LSTP PMOS

The entire package is also available here: PTM-MG

November 15, 2008:

PTM releases a new set of models for low-power applications (PTM LP), incorporating high-k/metal gate and stress effect.

- 16nm PTM LP model: V2.1

- 22nm PTM LP model: V2.1

- 32nm PTM LP model: V2.1

- 45nm PTM LP model: V2.1

September 30, 2008:

PTM releases a new set of models for high-performance applications (PTM HP), incorporating high-k/metal gate and stress effect.

- 16nm PTM HP model: V2.1

- 22nm PTM HP model: V2.1

- 32nm PTM HP model: V2.1

- 45nm PTM HP model: V2.1

February 29, 2008:

PTM releases the model for metallic carbon nanotube (CNT-interconnect).

- Verilog-A based model card for CNT-interconnect is available at post-si

October 29, 2007:

PTM releases a new version for sub-45nm bulk CMOS, providing new modeling features of metal gate/high-k, gate leakage, temperature effect, and body bias.

- 22nm PTM model for metal gate/high-k CMOS: V2.0

- 32nm PTM model for metal gate/high-k CMOS: V2.0

- 45nm PTM model for metal gate/high-k CMOS: V2.0

July 30, 2007

PTM extends the effort to post-Si devices. The first release is for carbon nanotube FET (CNT-FET).

- Verilog-A based model card for CNT-FET is available at post-si

December 15, 2006

PTM for bulk CMOS is released, for 22nm node.

- 22nm BSIM4 model card for bulk CMOS: V1.0

February 22, 2006

A new generation of PTM for bulk CMOS is released, for 130nm to 32nm nodes. It captures the latest technology advances and achieves better scalability and continuity across technology nodes.

- 32nm BSIM4 model card for bulk CMOS: V1.0

- 45nm BSIM4 model card for bulk CMOS: V1.0

- 65nm BSIM4 model card for bulk CMOS: V1.0

- 90nm BSIM4 model card for bulk CMOS: V1.0

- 130nm BSIM4 model card for bulk CMOS: V1.0

September 30, 2005

- 32nm BSIM4 model card for bulk CMOS: V0.0

- 32nm sub-circuit model for FinFET (double-gate): V0.0

- 45nm sub-circuit model for FinFET (double-gate): V0.0 [for better convergence in the simulation, you can initialize the node voltage when using PTM for FinFET]

July 31, 2002

- 45nm BSIM4 model card for bulk CMOS: V0.0

- 65nm BSIM4 model card for bulk CMOS: V0.0

May 31, 2001

Cnt Fet Review

- 90nm BSIM3 model card for bulk CMOS: V0.0

- 130nm BSIM3 model card for bulk CMOS: V0.0

- 180nm BSIM3 model card for bulk CMOS: V0.0

Cntfet Ppt

References

Carbon Nanotube Fet

- S. Sinha, G. Yeric, V. Chandra, B. Cline, Y. Cao, 'Exploring sub-20nm FinFET design with predictive technology models,' to be published at DAC, 2012.

- A. Balijepalli, S. Sinha, Y. Cao, 'Compact modeling of carbon nanotube transistor for early stage process-design exploration,' ISLPED, pp. 2-7, 2007.

- W. Zhao, Y. Cao, 'New generation of Predictive Technology Model for sub-45nm early design exploration,' IEEE Transactions on Electron Devices, vol. 53, no. 11, pp. 2816-2823, November 2006.

- Y. Cao, T. Sato, D. Sylvester, M. Orshansky, C. Hu, 'New paradigm of predictive MOSFET and interconnect modeling for early circuit design,' pp. 201-204, CICC, 2000.